<ALD(Atomic Layer Deposition)>

- 개념

SLG(Self-Limiting Growth) 방식으로 원자층을 한층 한층 쌓아 올려 막을 형성하는 방법

- 방식

- self-limited growth

웨이퍼 프로세싱 시에 아무리 소스를 많이 공급을 해도 원자층은 1개 층만 쌓이는 것을 의미

- 특징

1. conformality가 좋음

2. 원자 scale에서 두께 조절이 쉬움

3. atomic 수준의 조성 제어가 가능

4. large area uniformity

5. CVD보다 작은 불순물

6. CVD보다 낮은 성장 온도

- 활용

- 나노 스케일 3D 구조의 경우, 높은 AR로 증착할 수 있는 기능이 필요

-> ALD가 유일한 해결책!

- HIGH-K 기반 나노 라미네이트 - 최신 DRAM 구조의 표준 소재

- 로직 소자 제작 공정

- DRAM 메모리 소자 제작 공정

- VNAND Flash 메모리 소자 제작 공정

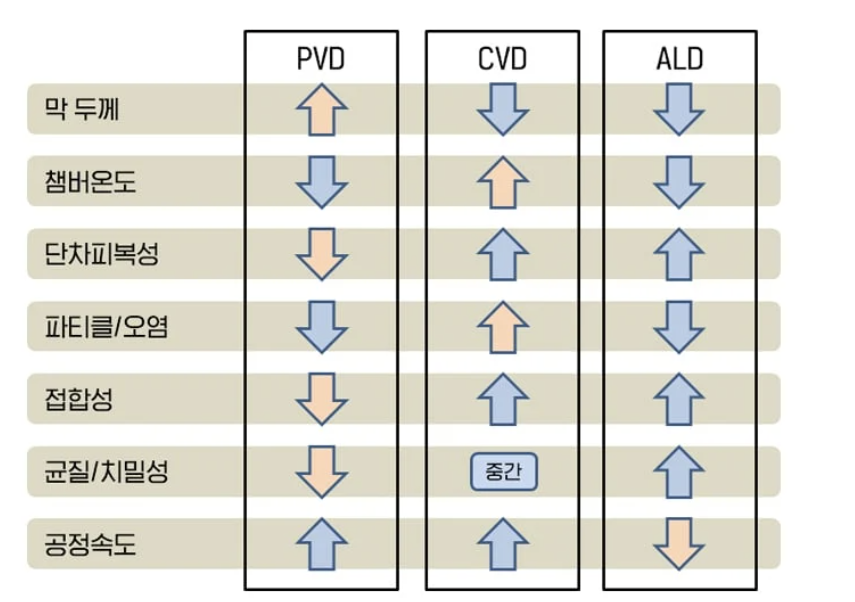

- ALD와 다른 공정의 비교

- ALD 박막의 성장 특성

- saturated GPC

precursor 또는 reactant에 노출시켰을 때, 박막의 두께가 증가하다가 특정 시간이 지나면 더이상 증가x

(∵chemisorption될 수 있는 분자가 제한적)

- Areal coverage

어떠한 legand인자에 따라 성장률이 다름

- steric hindrance

precursor의 부피가 크면 표면에 부착된 다른 precursor에 의해 간섭이 발생

-> adsorption sites가 100% 채워지는 것이 불가능

- process window

1) condension

전구체가 반응물과 반응하지 않고 그대로 쌓이는 경우

2) small thermal E

전구체의 활성화 에너지가 부족해서 붕완전한 반응 발생

3) decomposition

너무 높은 온도로 인해 열에너지가 커져서 SLS가 일어나지 않고 모두 증착

4) desorption

높은 온도에 의해 이미 증착된 막의 원자들이 탈착

https://news.skhynix.co.kr/post/ald-using-atoms

[반도체 특강] ALD, 원자를 이용해 박막을 만드는 방법

트랜지스터가 점유하는 체적을 지속적으로 축소시키기 위해서는 표면을 둘러싸고 있는 막의 두께를 줄여야 합니다

news.skhynix.co.kr

<PE-ALD(Plasma Enhanced Atomic Layer Deposition)>

- 장점

- 높은 반응성

-> 기존의 ALD에서 되지 않는 반응성이 낮은 precursor 가능

- 높은 증착 속도

- 낮은 deposition 온도

- 좋은 막질

- 핵형성이 잘됨

-> 박막 형성을 빠르게 하는 데 중요!

- 단점

- film에 손상을 줄 수 있음

- step coverage가 좋지 않음

-> shadowing effect, recombination effect 발생 가능

<ALD 장비>

- traveling wave type

- 가장 간단한 유형의 reactor 구성

- laminar flow mode 에서 가스가 측면으로 흐름

- shower head type

- 높은 반응 속도

- damage 발생 가능

(∵ ion and electron bombardment)

- CCP 방식

- remote type

- 'shower head type'의 damage 문제 개선

- ICP plasmam 사용

- 제한된 산업용 사용

- bias가 없기에 가속x

-> 성장률이 좋지 않음

- batch type

- 처리량 증가

- 대면적 가능

- spatial type

- 4배 증가된 생산성

- 입자 형성 없이 대면적 균일 코팅

- R2R type

<AS-ALD(Area Selective Atomic Layer Deposition)>

- 개념

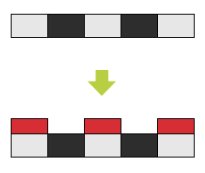

- self-alinged fabrication을 활용한 영역 선택적 원자층 증착

- 옴스트롱 단위의 정밀도로 wafer 표면에 선택된 특정 영역에만 박막 물질을 화학적으로 증착하는 bottom-up 공정

- 박막에 사용되는 화학 물질인 전구체 설계에 따라 결

- 활용

FAV(Fully Alinged Via)에서 edge placement error가 발생하면 RC delay로 인한 신뢰성 하락

-> 해결방안 ) AS-ALD

https://news.skhynix.co.kr/post/as-ald-technology

나노 스케일의 더 작은 반도체 소자 제작을 위한 AS-ALD 기술

반도체 소자의 미세화로 트랜지스터 밀도는 크게 증가하게 되었고, 이를 통해 컴퓨터에서부터 스마트폰에 이르기까지 다양한 IT 제품의 성능을 향상시켜왔다. 이렇게 진화되는 미세화 과정에서

news.skhynix.co.kr