<금속 배선>

- 요구 조건

- 낮은 면저항

-> voltage drop과 propagation delay 최소화

- 열적 안정성이 좋아야 함

- 식각 선택성 좋아야 함

- oxide에 부착성이 있어야 함

- 장기간 신뢰성이 높아야 함

- barrier의 사용

- metal-semiconductor 접합

- ohmic 접합

semicontuctor에서 metal로 양방향 이동

- schottky 접합

semicontuctor에서 metal로 한방향 이동

-> off상태시, 전하 수송이 어려움

<Al금속의 배선으로서의 특성>

- 특징

| 장점 | 단점 |

| - 상대적으로 값이 저렴 - SiO2에 대한 부착성이 좋음 - 낮은 면저항 - deposit과 etching 쉬움 |

- junction spiking - electromigration - 부식 - 낮은 녹는점 |

- junction spiking

- Al-Si binary system의 공융 특성에 의해 P-N접합부로의 Al 침투

- Al이 Si와 접촉할 때마다, Si는 어닐링 중에 Al에 용해

=> 해결방안

- 합금에 포함된 Si의 양이 용해도 요건을 만족할 때까지 공증발하여 Al에Si를첨가하는것

- Al 기판과 Si기판 사이에 장벽 금속층(ex)TiN)을 도입

- electromigration

- 전도 전자로부터의 운동량 전달로 인한 금속 원자의 이동 (전기장으로 인한 금속 이온의 강제 이동)

- 금속 원자(이온)는 전도체(ion wind)의 양극단으로 이동하는 반면 빈 공간은 음극단으로 이동

- 접촉의 궁극적인 손실 또는 회로의 고장을 야기함으로써 집적회로의 신뢰성을 저하

=> 해결방안

- 소량의 Cu 첨가

-> 전자 이동의 저항성 증가

- 대나무 구조

- blech length를 길게

<Cu금속의 배선으로서의 특성>

- 배경

금속선의 선폭이 점점 줄어듦(Down Scaling)에 따라, 50nm 이하의 High Tech.에서는 더 이상 알루미늄을 사용하기 어려워짐

- Al과 Cu의 비교

- 특징

| 장점 | 단점 |

| - 높은 전도성 - CVD, PVD 가능 |

- Dry etching 불가 |

- Dry etching 불가

(∵ 식각 시 발생하는 화학물이 가스 형태로 배출돼야 한느데, 구리 화합물은 휘발이 안됨)

=> 해결방안 ) Damascene technology + CMP

damascen 방식이 완료된 후에도, 불필요한 구리를 제거하기 위해 식각이 아닌 CMP(Chemical Mechanical Polishing, 화학적 기계적 연마) 방식으로 연마(Polishing)

https://news.skhynix.co.kr/post/damascene-process

[반도체 특강] 다마신 구리 배선 방식_ 알루미늄의 한계를 극복하다

구리를 전해도금(Electroplating) 방식으로 채우는 다마신(Damascene) 공정이 새롭게 개발되면서 10nm(나노미터)의 선폭까지 구현이 가능해졌고, 이로써 구리 재질은 오래 사용해도 선폭이 유지될 수 있

news.skhynix.co.kr

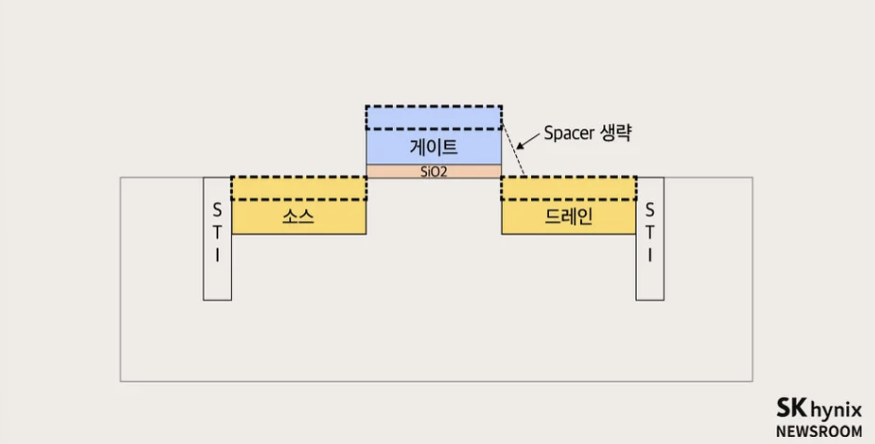

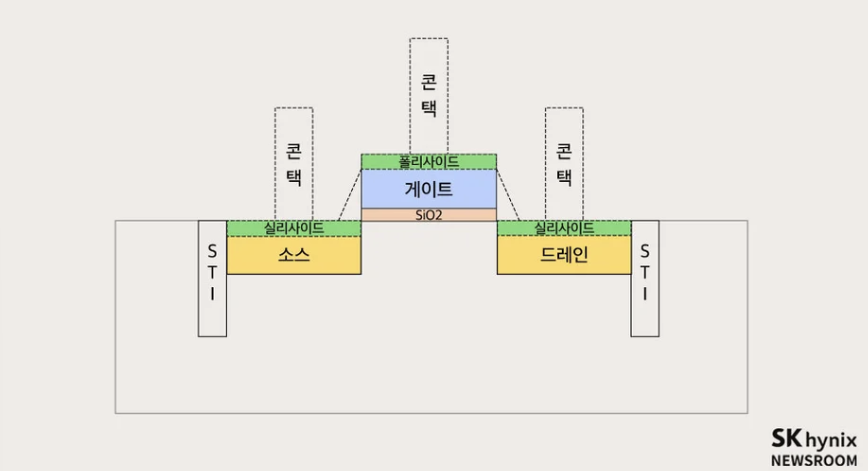

<Salicide>

- 개념

금속 입자가 실리콘 격자 속으로 확산해 '실리사이드'층을 자동으로 형성하는 공정

- 필요성

- metal-Si 화합물은 낮은 저항성과 함께 높은 열적 안정성을 가짐

- poly-Si 및 확산 상호 연결의 저항을 줄이기 위해 사용

- 방식

1. 실리사이드(Silicide)층 설치 준비

(silicide : 실리콘과 금속 원소의 혼합물)

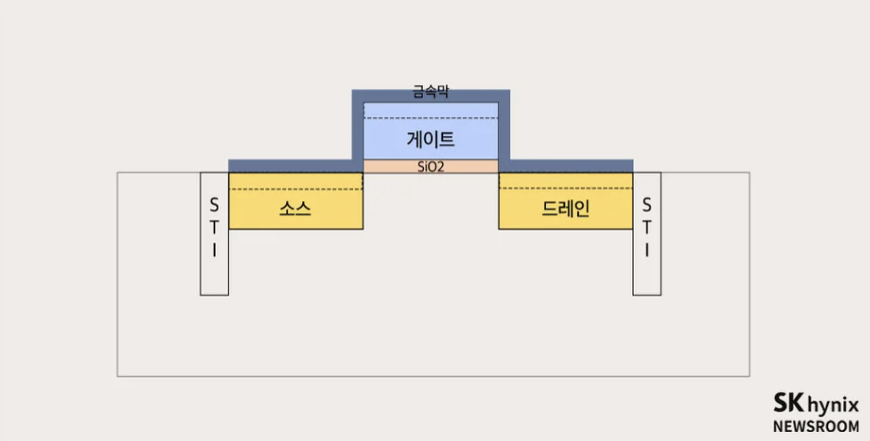

2. 금속막 증작

PVD(Physical Vapor Deposition) 공정에서 스퍼터링(Sputtering) 방식을 이용해 웨이퍼 전면에 금속막을 증착

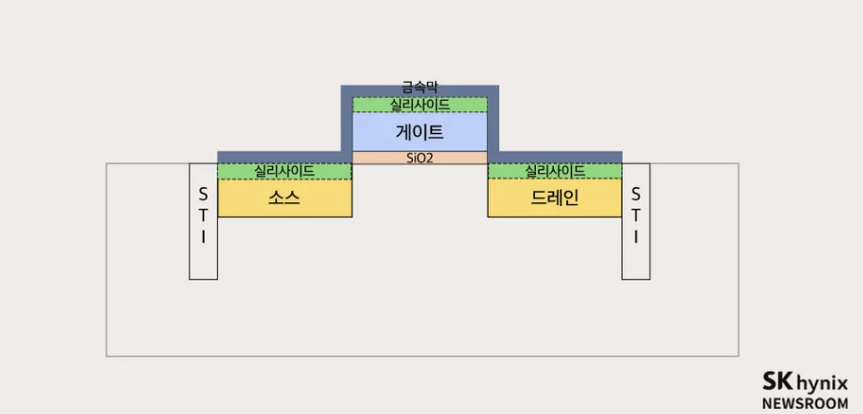

3. 실리사이드 (silicide)층 형성

금속막을 증착한 뒤 어닐링 방식(RTA)으로 열에너지(섭씨 500~900도)를 인가

-> 금속 원소가 하부 막질로 확산해 격자를 구성하고 있는 실리콘 원자들과 결합

-> '실라사이드'라는 층 형성

4. 금속막 제거(Strip)

상부에 존재하는 금속층(PVD나 CVD로 증착)은 이제 쓸모가 없어지므로 식각을 통해 제거

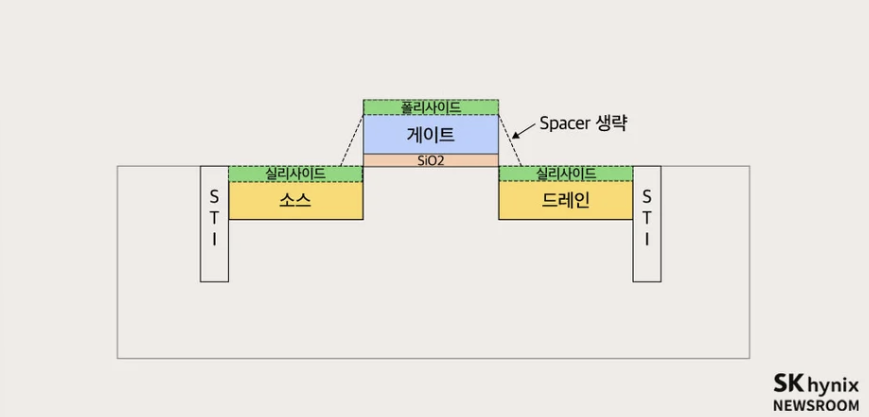

5. 실리사이드(silicide)층 완성

2차 RTA(1차와 유사한 온도 조건)를 진행해 실리사이드 및 폴리사이드가 확고하게 자리 잡을 수 있도록 함

-> 실리사이드층이 웨이퍼 표면에 드러나면, 그 상부에 금속성 재질로 연결되는 콘택(Contact)을 연결

https://news.skhynix.co.kr/post/self-alignment_silicide

[반도체 특강] 살리사이드(Salicide), 공정을 단축하다

금속배선 공정 중 가장 먼저 실시하는 ‘살리사이드(Salicide)’란 Self-Alignment(자체 정렬)와 Silicide(실리사이드)의 합성어로, 금속 입자가 실리콘 격자 속으로 확산해 실리사이드층을 자동으로 형

news.skhynix.co.kr