<MOSFET 구조 및 공정>

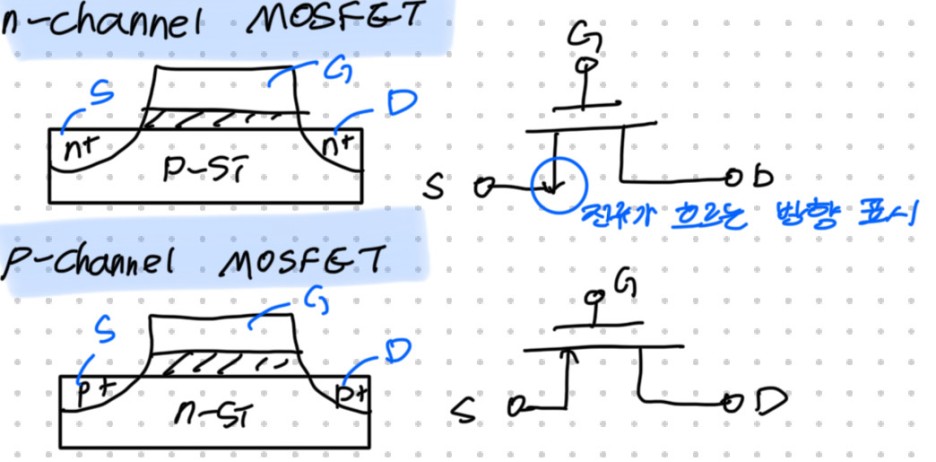

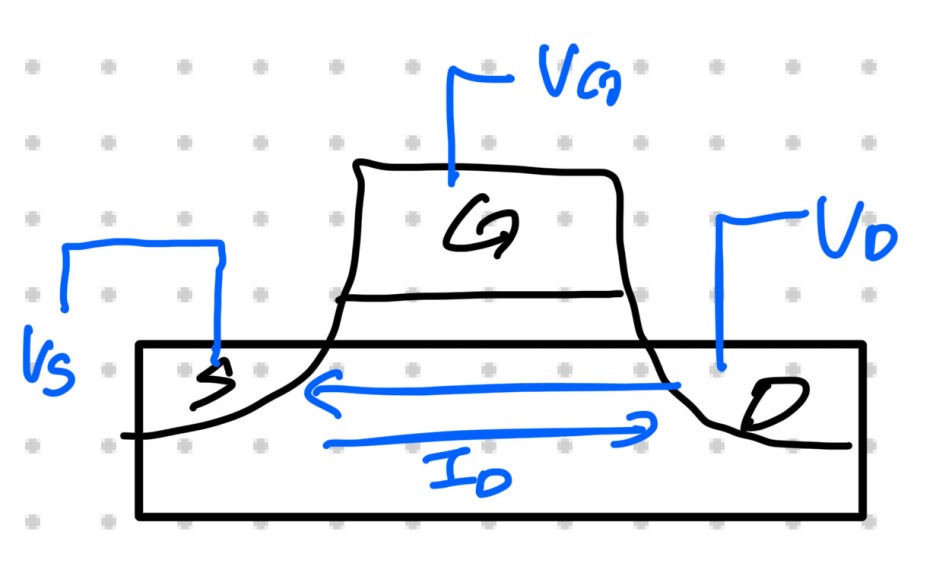

[MOSFET 구조]

- Gate

전자의 흐름 유무를 조절

- Source

전하의 공급원

- Drain

전하가 빠져나가는 곳

=> 전하가 이동하기 위해서는 source와 drain사이의 전위차가 필요!

[MOSFET 제조 공정]

<n-channel MOSFET>

- P형 기판 위 초박막 SiO2 증착 후, high-k 절연막 적틍

- 금속 gate 적층 뒤, 이방성 RIE 식각

- source와 drain에 n+이온 impalnt

- 어닐링

- 금속 배선 공정을 통해 MOSFET간 연결하여 chip 완성!

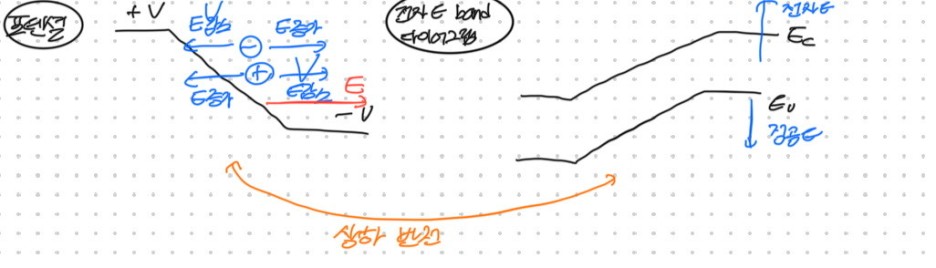

<에너지 밴드 다이어 그램>

[전자 에너지 밴드 다이어그램]

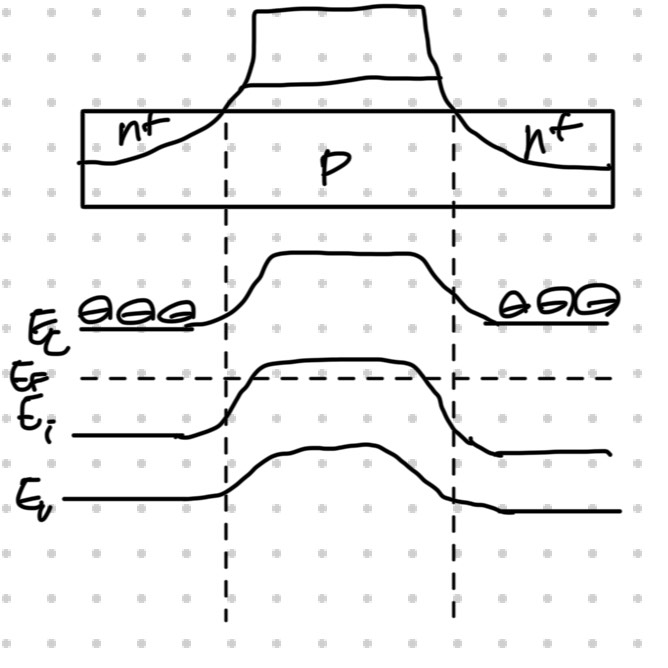

[MOSFET에서의 에너지 밴드 다이어그램]

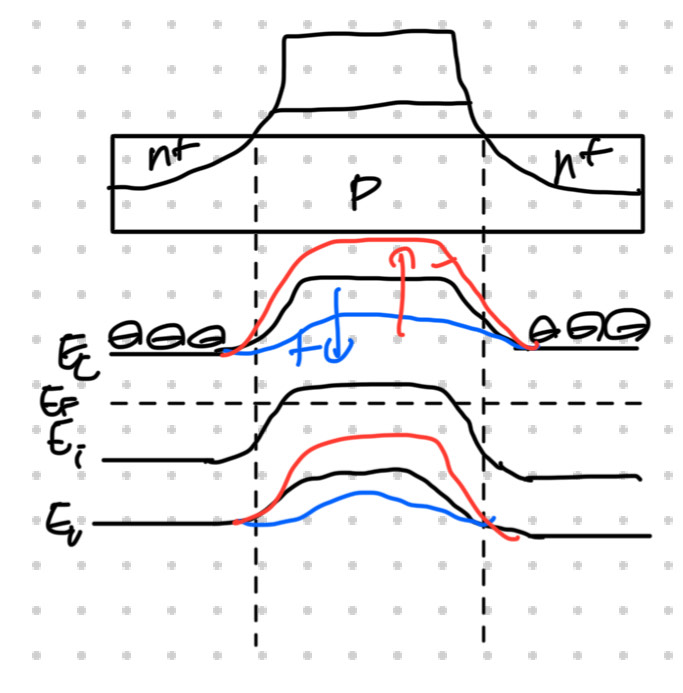

<n-channel MOSFET>

- 평형 상태

전자가 source에서 drain으로 이동하는 데 있어서 포텐셜 장벽 발생 → Drain에서 Source로의 전류 흐름이 없음

- Gate에 (+) 전압이 가해짐

gate쪽의 포텐셜 장벽이 조정되어 (-) 전하가 유도

→ 유도된 전자들이 FET의 channel을 형성

→ Drain에서 Source로의 전류 흐름이 발생

=> gate에 (-)전압이 가해지면 포텐셜 장벽이 높아지게 되어 전하가 움직이지 못하고,

gate에 (+)전압이 가해지면 포텐셜 장벽이 낮아져서 전하가 움직임

<Linear 영역과 saturation 영역>

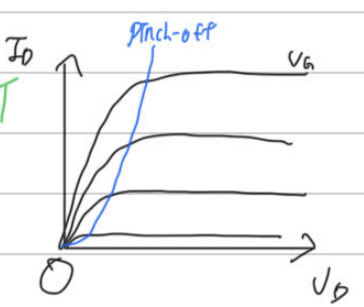

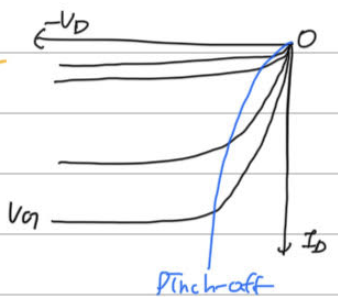

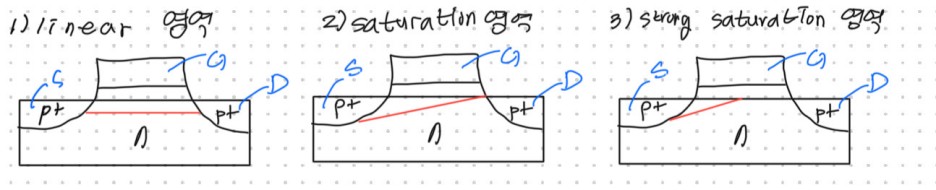

[ID-VD 특성에서의 MOSFET 동작 영역]

VG를 고정시키고, VD를 변화시키며 ID값 확인

<n-channel MOSFET>

<p-channel MOSFET>

- linear 영역 (VD < VG-VT)

VD가 증가할수록, ID가 선형적으로 증가

- saturation 영역 (VD > VG-VT)

VD가 증가해도, ID가 변화X

=> 문턱전압 (VT = VD - VG)

채널을 유도하는 데 필요한 최소한의 gate 전압

(이하 - channel 켜지지x, 이상 - channel이 켜짐)

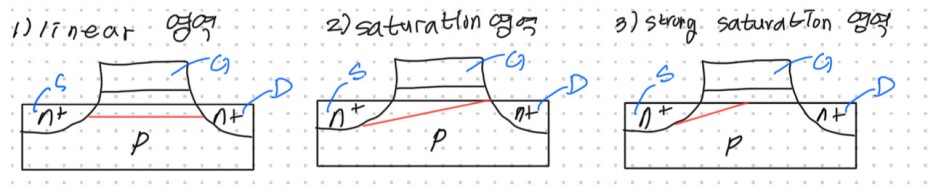

[채널 Pinch-off]

<n-channel MOSFET>

<p-channel MOSFET>

- linear 영역

작은 크기의 VD가 가해질 때, source쪽과 drain쪽의 channel에 비슷한 양의 전하가 channel을 형성

- saturation 영역

VD가 더 증가하여 VG-VD=VT가 되면, drain쪽에서는 VT가 겨우 유지되게 되어 '채널 pinch-off' 발생

- strong saturation 영역

pinch-off가 발생하고도 VD가 더 증가하게 되면, pinch-off 지점은 source쪽으로 더 이동

=> VD가 증가할수록, channel에 더 많은 전하가 유도되어 channel은 더 큰 전도도를 가지게 됨!

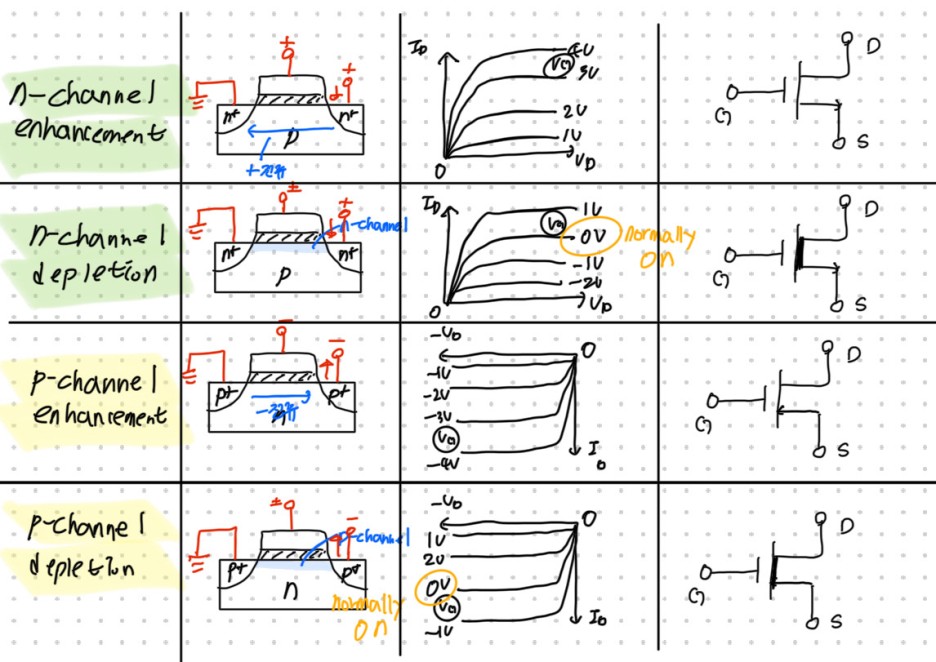

<채널에 따른 MOFSET 종류>

'MOSFET' 카테고리의 다른 글

| Short Channel Effect (0) | 2024.01.26 |

|---|---|

| 문턱전압조절 (0) | 2024.01.26 |

| MOSFET ID-VD 특성 / ID-VG 특성 (0) | 2024.01.26 |

| MOS cap C-V 특성 (0) | 2024.01.26 |

| 이상적인 MOS cap (0) | 2024.01.26 |