<C-V 특성>

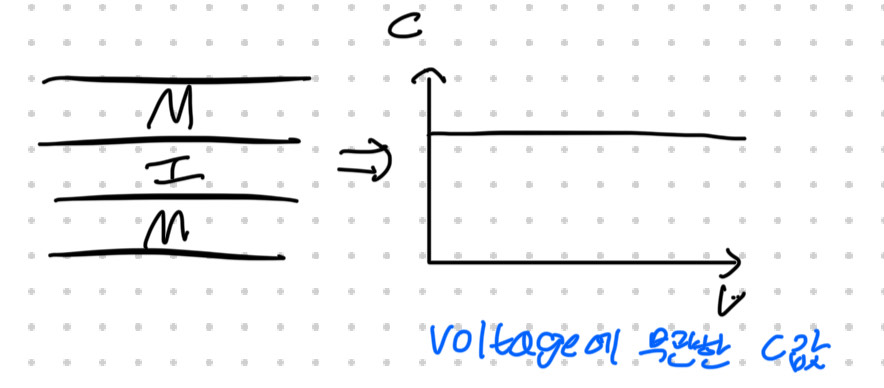

[MIM parallel plate capacacitor의 C-V특성]

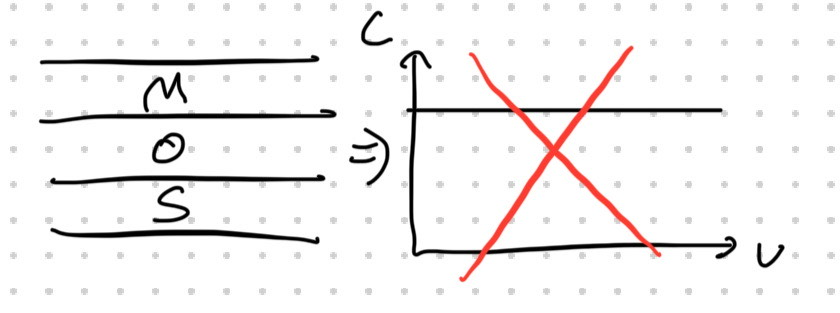

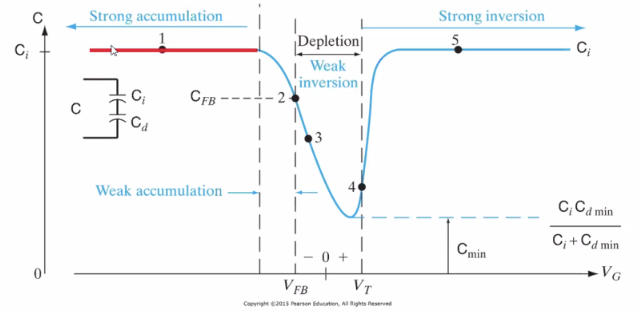

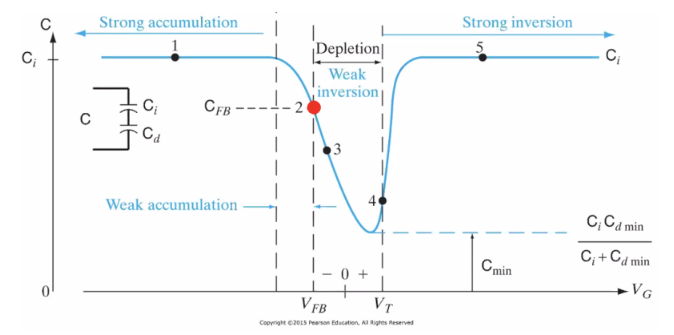

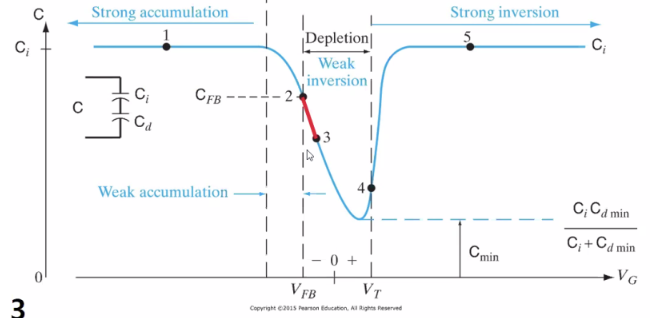

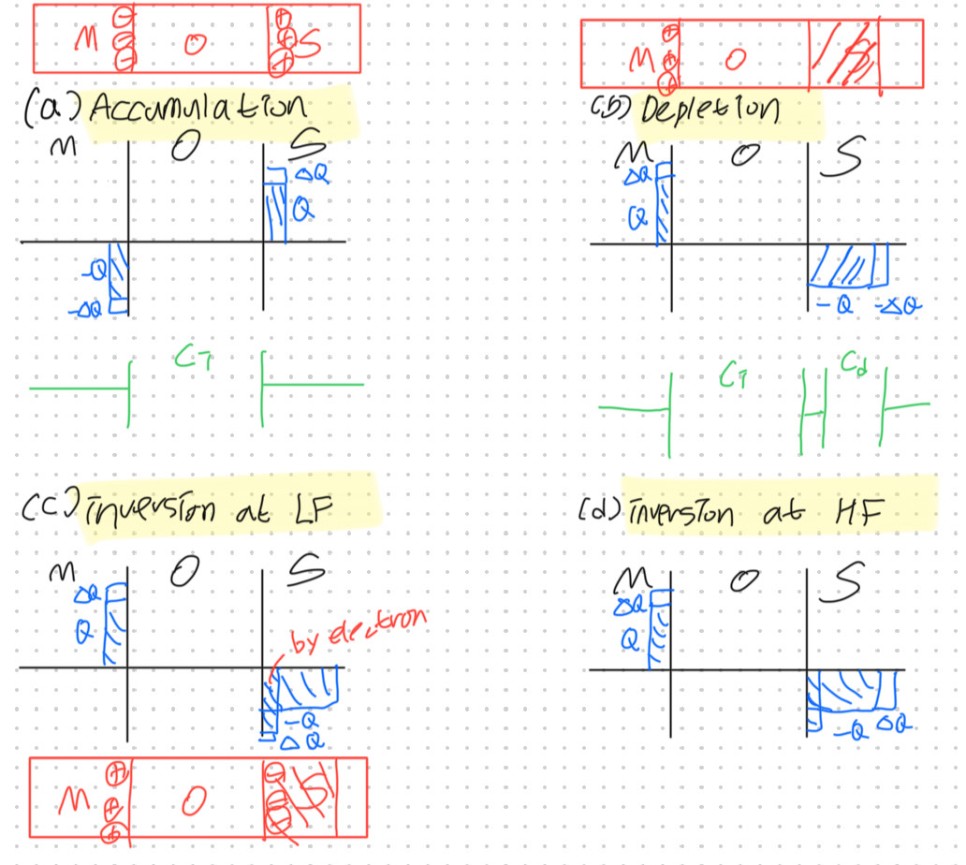

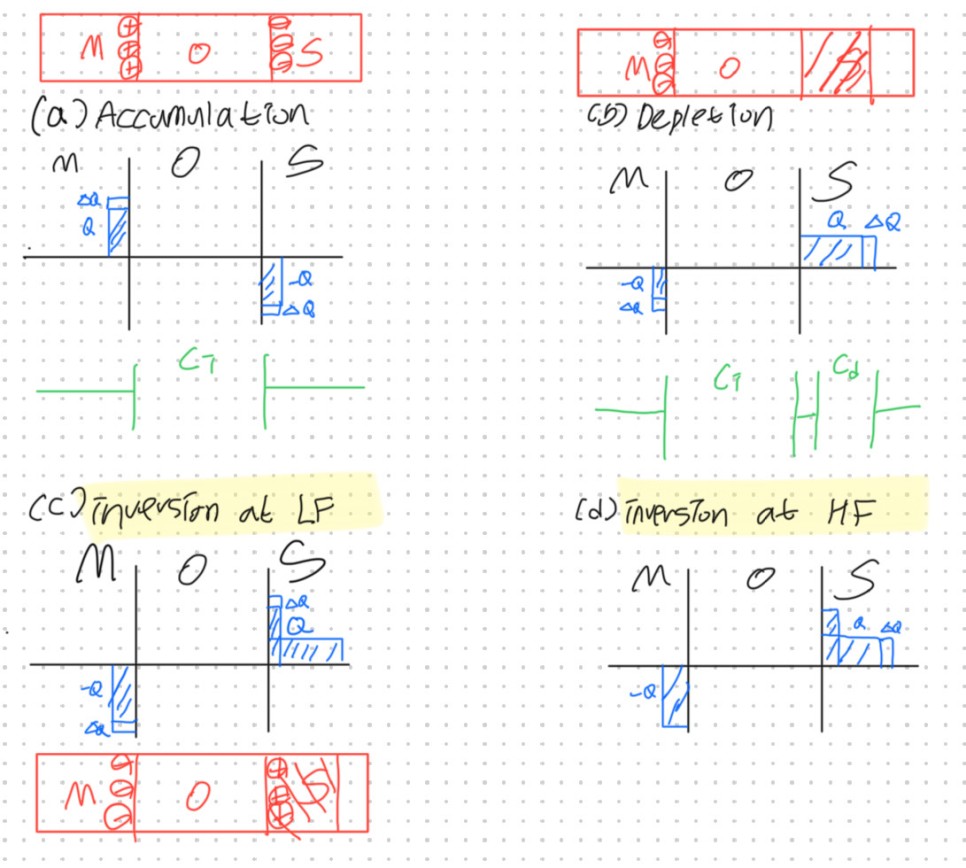

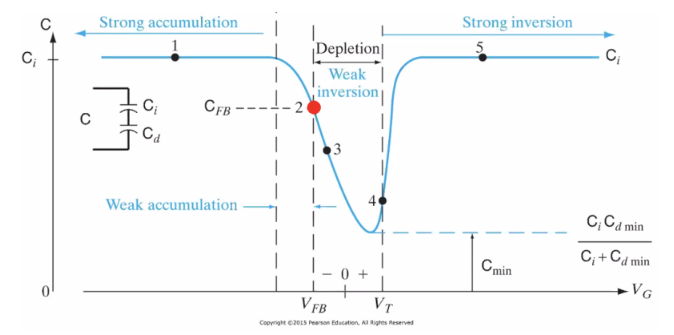

[MOS capacacitor의 C-V특성]

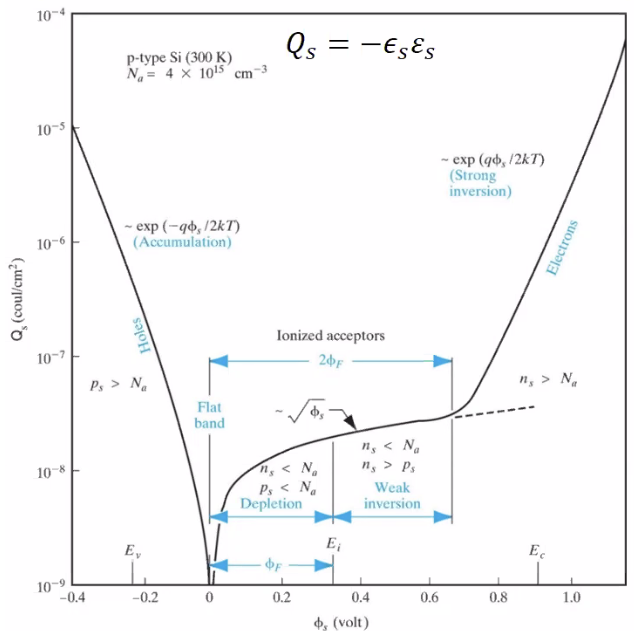

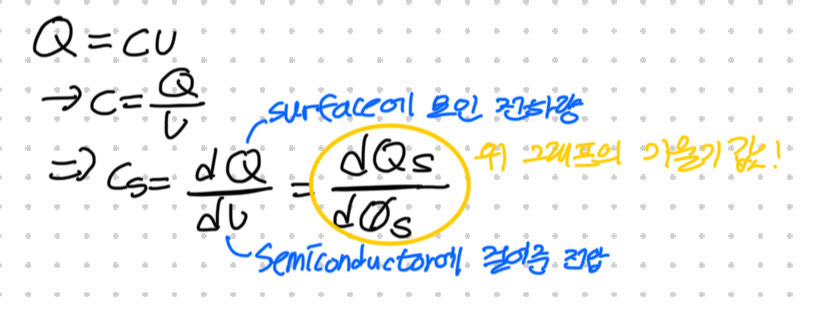

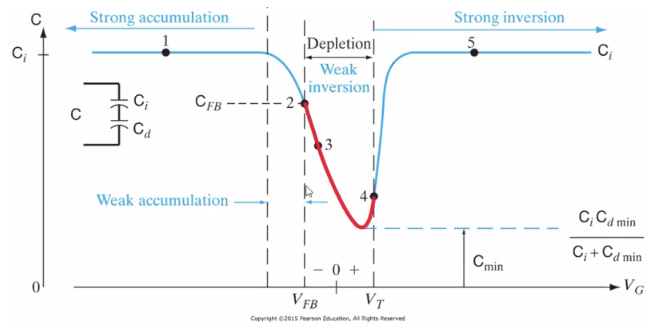

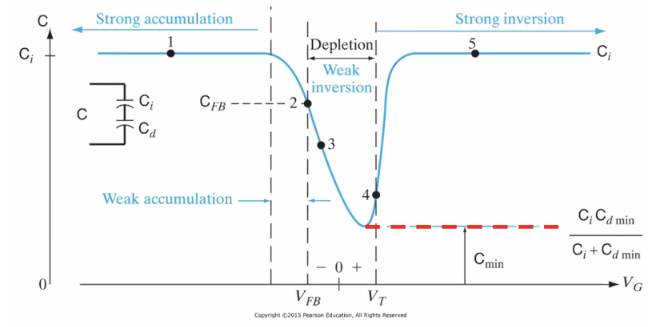

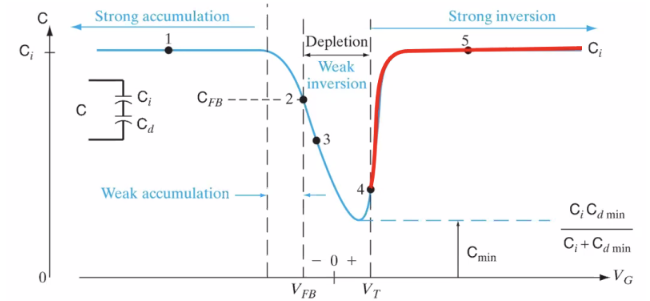

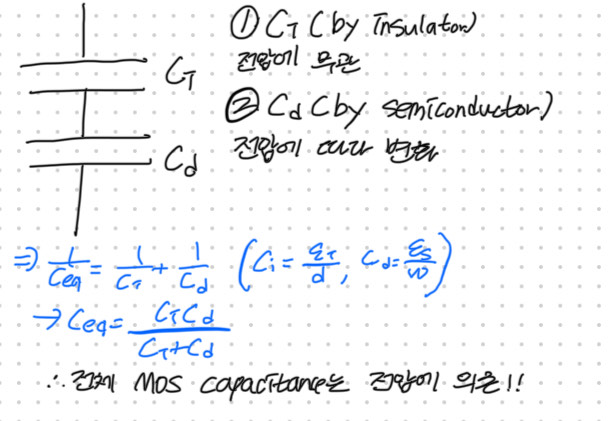

=> MOS cap의 C-V 특성은 반도체 표면이 어떤 영역(accumulation, depletion, inversion)인지에 따라 달라짐

<n-channel MOSFET>

- strong accumulation

정공이 표면에 축적

-> 절연층 특성에 의해 결정

2. flat band

에너지 밴드가 평평해짐

3. weak inversion

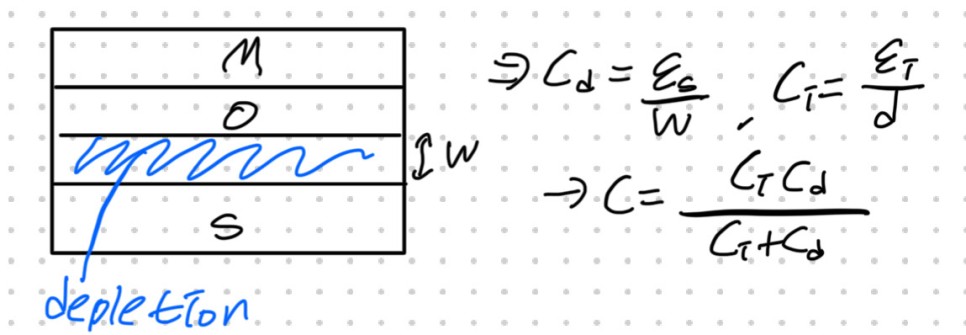

전압이 증가하면서 depletion이 발생하면, depletion층 capacitance Cd가 Ci에 직렬로 추가가 됨

4. depletion + weak inversion

전압이 증가

-> flat band에서 weak inversion을 지나 strong inversion에 도달할 때까지 W가 커짐

-> Capacitance감소

5.1. strong inversion at high frequency

inversion층의 전하가 입력 신호의 변화를 따라갈 수 없음

-> capacitance가 최솟값

5.2 strong inversion at low frequency

소수캐리어인 전자가 계면에 모임

-> 절연막 관점에서 보았을 때 유전막의 두께가 얇아지는 효과를 가짐

<p-channel MOSFET>

[전하 반응 위치에 따른 C-V 특성]

<n-channel MOSFET>

<p-channel MOSFET>

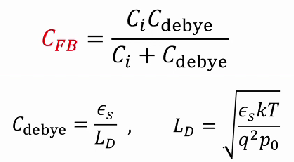

<실제 표면의 영향>

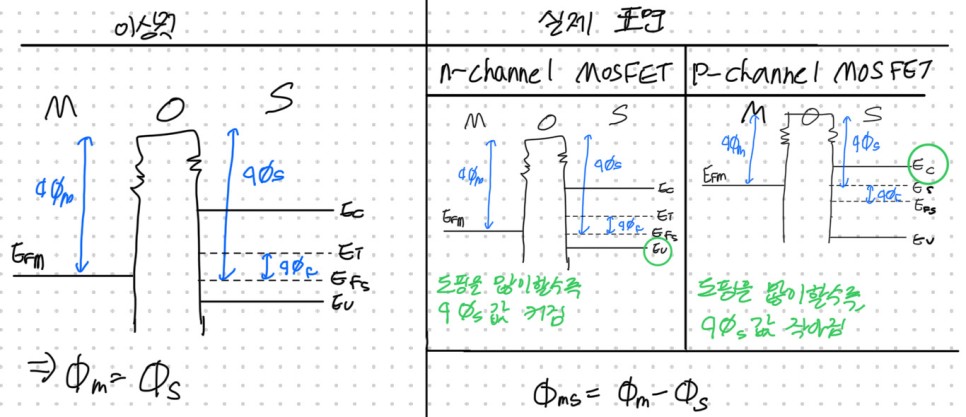

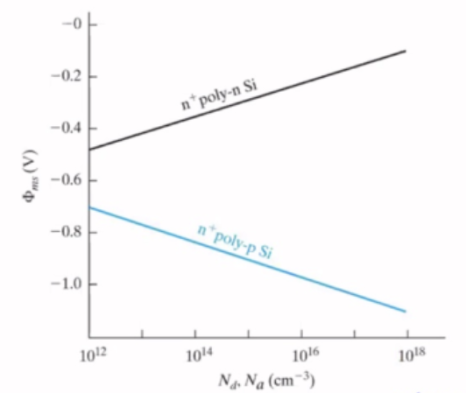

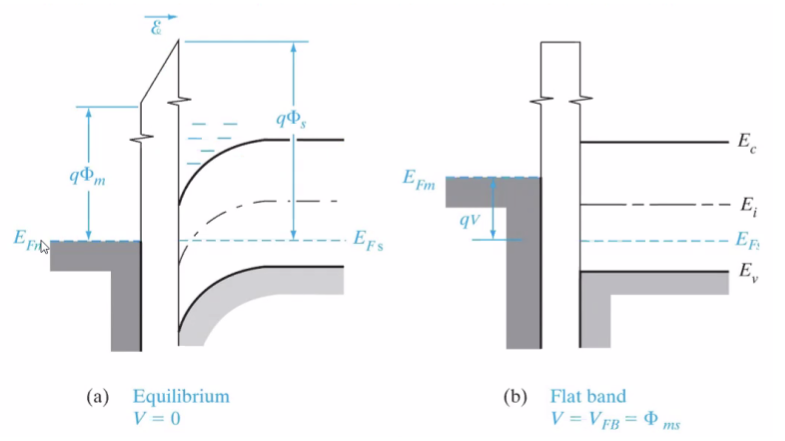

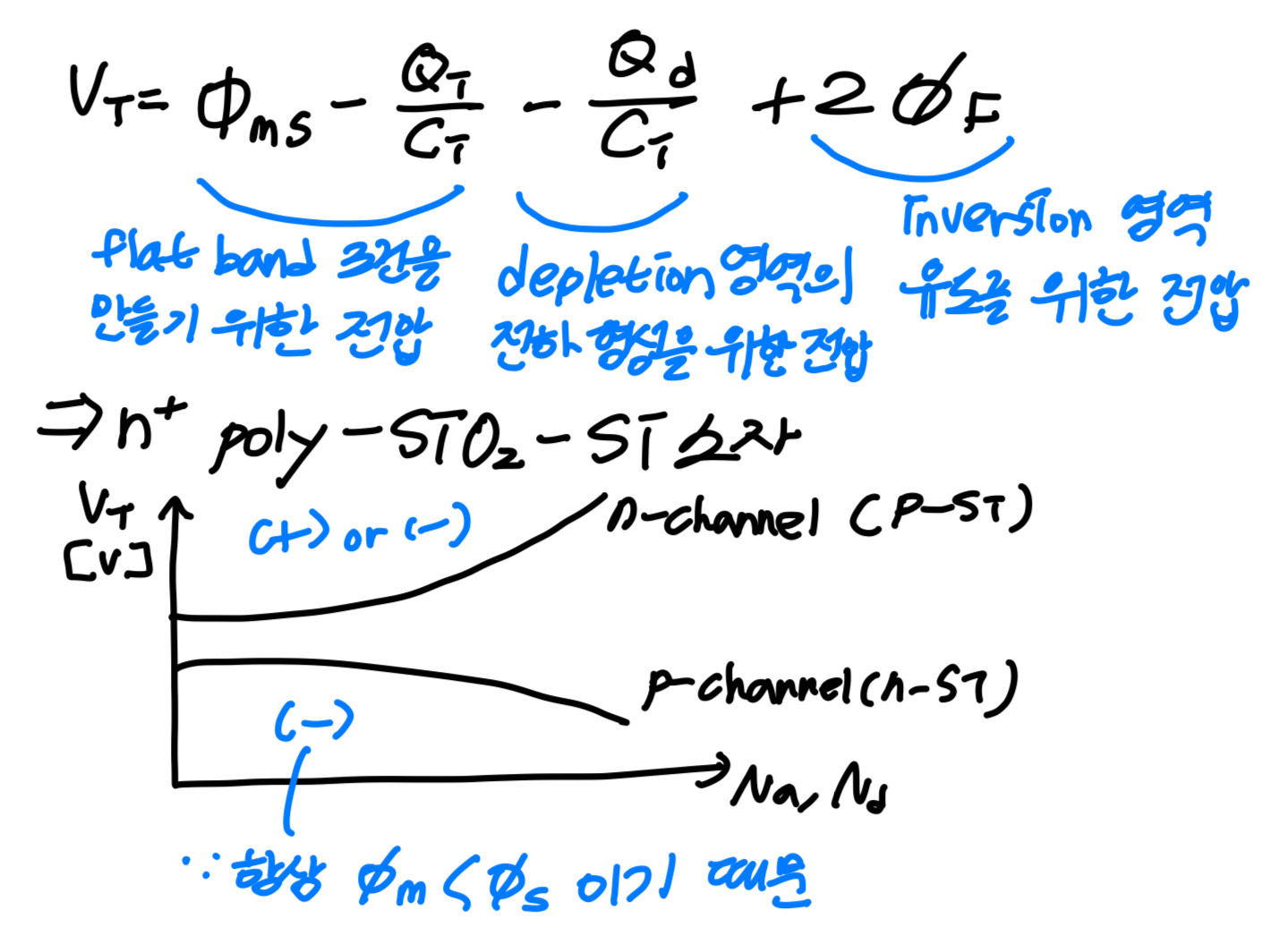

[Work function 차이]

=> (a) equilibrium

p-type의 경우, ΦMs < 0

-> 평형 상태에서 금속이 (+), 반도체 표면이 (-) 전하를 띰

(b) flat band

flat band 조건이 되기 위해서는, 금속에 음의 전압을 인가해줘야 함

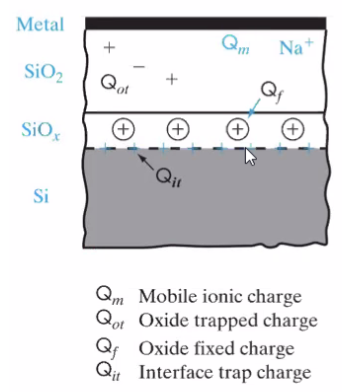

[interface 전하]

실제 표면에서는 다음과 같이 oxide가 존재!

1) Mobile ionic 전하

- 양전하

- 알칼리 금속 이온 (Na+)이 산화 등의 공정 과정 중 불가피하게 발생

- 해결방안) ex) clean room에서 방진복 입기

2) oxide trapped charge

- 양전하 또는 음전하

-SiO2의 불완전함으로 인해 존재

3) Oxide fixed charge

- 양전하

- interface근처에는 fixed charge를 가진 transition층이 존재 (SiOx)

4) interfacde trap charge

- 양전하 또는 음전하

- 반도체 결정의 격자가 Si-SiO2 interface에서 갑자기 끊어지면서 발생

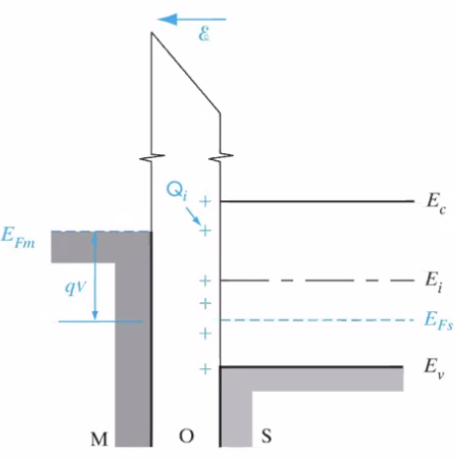

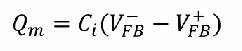

[effective interface 전하]

다양한 oxide 전하를 Qi에 포함

-> 이에 상응하는 음전하가 반도체에 유도가 되어야 함

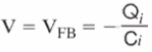

=>

<MOS C-V특성>

[문턱전압]

[절연층 두께와 최대 depletion폭]

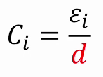

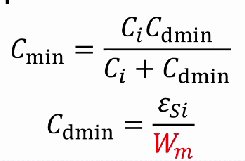

- 절연층 두께

accumulation 또는 저주파 strong inversion에서의 Ci를 통해 절연층 두께를 알 수 있음

- 최대 depletion 폭

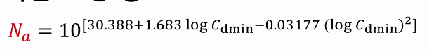

[기판 도핑 농도와 flat band capacitance, 전압]

- 기판 도핑 농도

- flat band capacitance

- flat band 전압

CFB일 때의 전압

[문턱전압]

VT가 정확하게 C-V 특성의 최소값에 대응되지 X

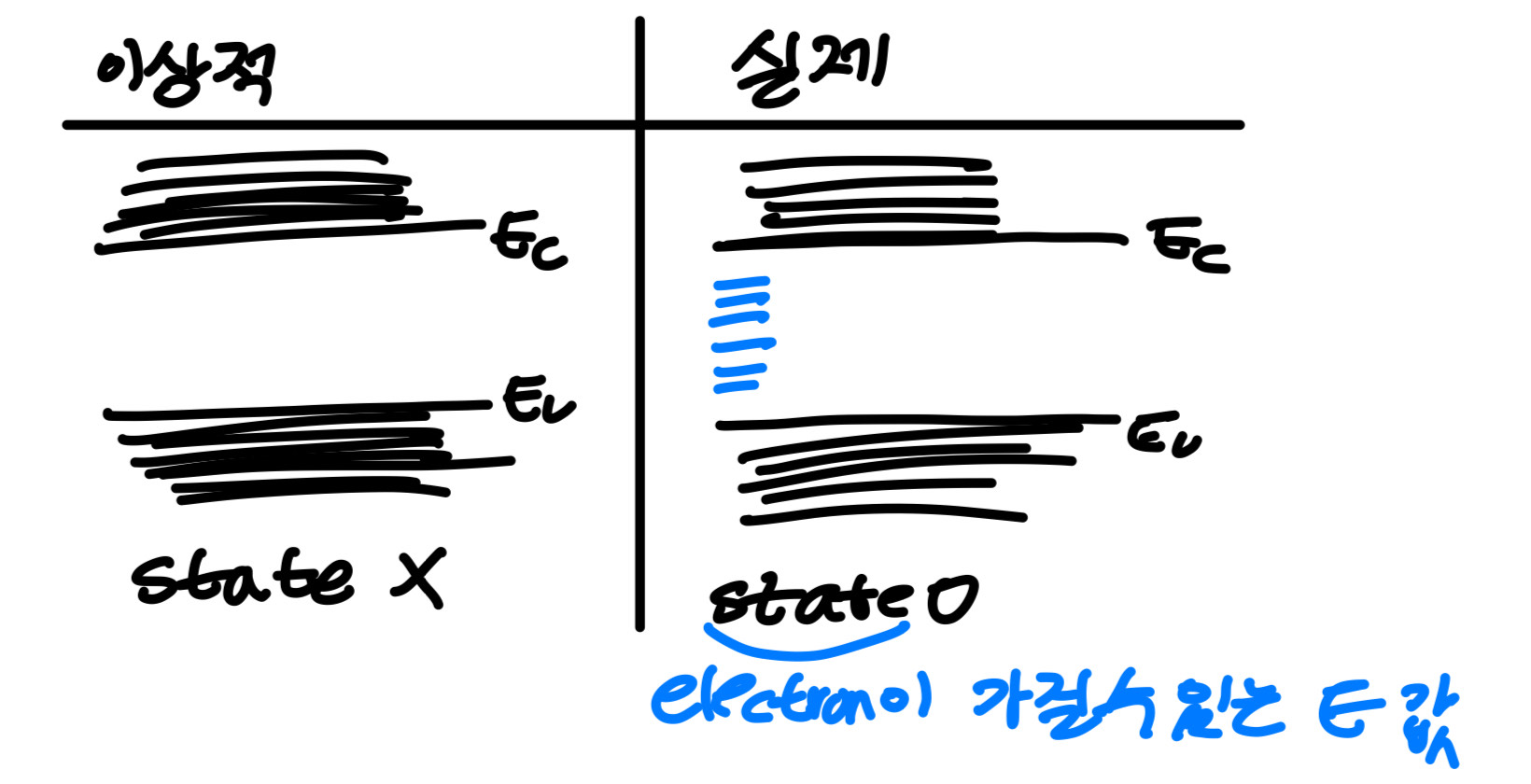

[Fast interface 상태밀도]

- 표면 포텐셜이 달라질 때, 전압에 따라 밴드갭 내의 fast interface 상태가 EF 위 / 아래로 움직일 수 있음

- 전하의 저장이 calacitance이기 때문에, 추가적인 Cit의 역할을 함

- fast inerface 상태는 아주 높은 주파수에서의 움직임을 따라갈 수 없음

-> CHF가 아닌 CLF에 기여

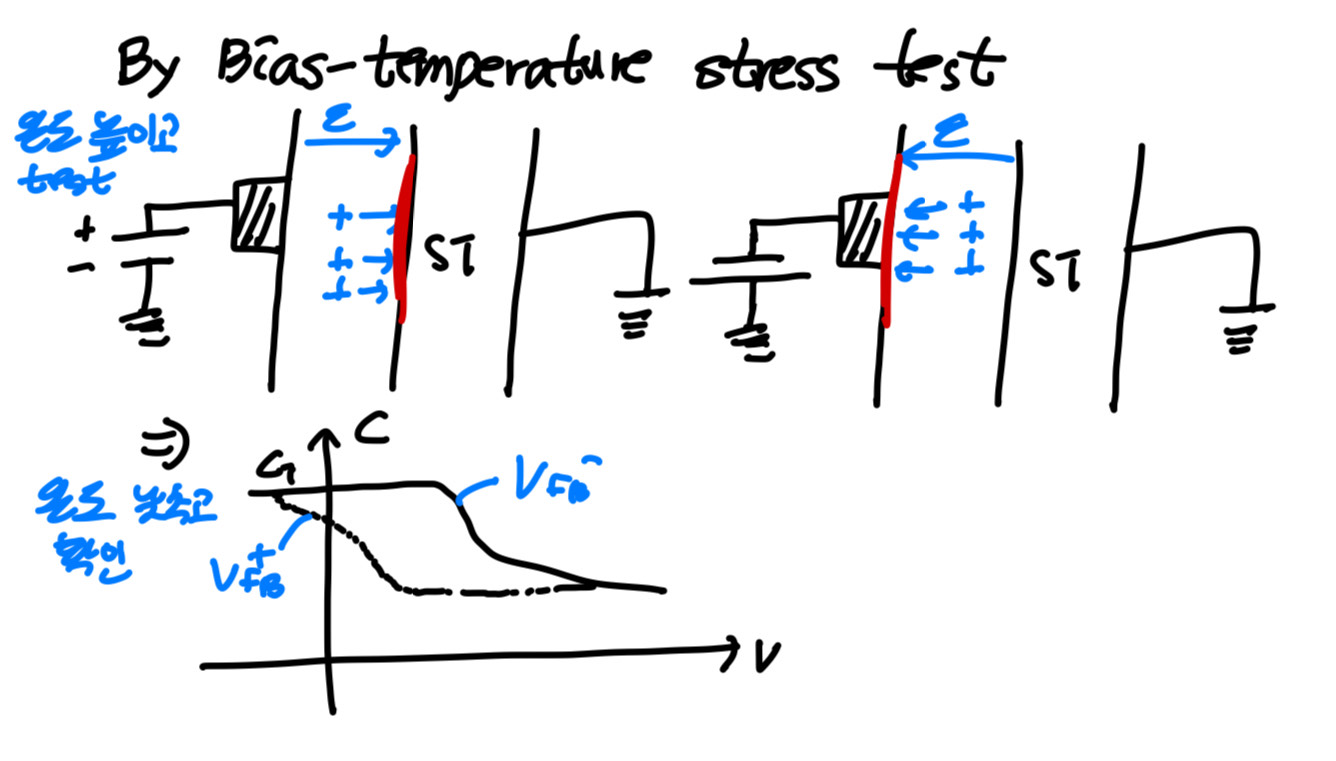

[Mobile ionic 전하]

- 이동성이 있는 이온이 gate 전압의 극성에 따라 절연막-Si inerface 또는 gate 전극으로 drift함

<MOS 절연막의 전류-전압 특성>

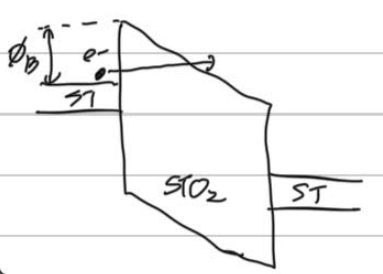

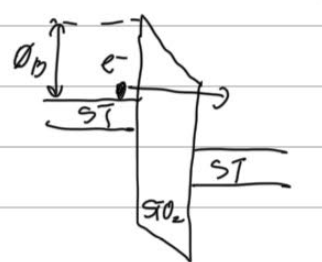

- 양자역학적 터널링

파동이 퍼텐셜 장벽을 뚫고 지나가는 양자역학적 현상

1) FN 터널링

oxide에 가해진 electron field가 강할때

2) Direct 터널링

oxide thickness가 매우 얇을 때

=> 작게만들면 누설 전류가 많아짐

-> 누설 전류를 줄이기 위해 high-K 사용

'MOSFET' 카테고리의 다른 글

| Short Channel Effect (0) | 2024.01.26 |

|---|---|

| 문턱전압조절 (0) | 2024.01.26 |

| MOSFET ID-VD 특성 / ID-VG 특성 (0) | 2024.01.26 |

| 이상적인 MOS cap (0) | 2024.01.26 |

| MOSFET 기본 동작 (0) | 2024.01.26 |