(4) LDD(Lightly Doped Drain) implantation

1.

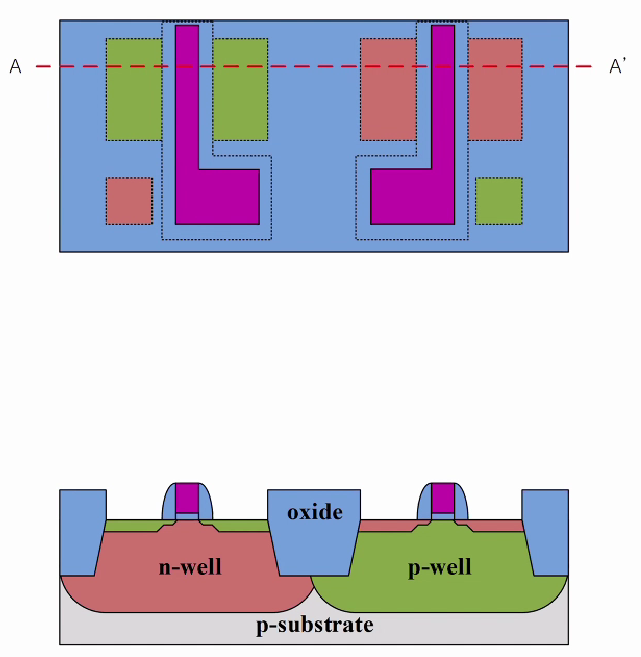

=> nsd(n-MOS source/drain) Mask

1) Photolithography

2) Ion implantation

- As, 20keV, 5x10^14cm^-2

3) PR strip

(cf) p-MOS의 body도 doping 진행!)

LDD

- 집적도가 향상됨에 따라 Channel Size가 점점 더 작아지고 Long Channel MOSFET에서는 크게 영향을 미치지 못했던 Pinch off 영역이 Short Channel MOSFET에서 강한 전기장에 의해 누설 전류를 유발하고, Hot Carrier Effect와 같은 SCE 효과를 극대화 시킴

-> 이를 억제하기 위해서 전기장을 완화활 필요가 있었고. Light한 Doping 농도의 Extension 영역을 형성

https://sshmyb.tistory.com/239

[반도체 전공정] CMOS Process Flow, 현직자도 꼭 한 번 숙지해야 하는 공정 플로우에 대해서 알아보자

안녕하세요! 딴딴교육생 여러분들, 오늘은 CMOS Process Flow에 대해서 다루어보겠습니다. 이전 포스팅에서도 한 번 다루었던 경험이 있습니다. 하지만 많은 분들이 CMOS 소자의 Cross Section을 많이 접

sshmyb.tistory.com

2.

=> psd(p-MOS source/drain) Mask

1) Photolithography

2) Ion implantation

- BF2, 20keV, 5x10^14cm^-2

3) PR strip

(5) HDD implantation

1.

1) SiO2(spacer) deposition

- PECVD or LPCVD

=> comformal한 증착 방법

- 저온 공정 (400도 이하)

(∵diffusion이 일어나면 Source/Drain이 가까워짐 -> 소자의 특성에 큰 영향_

2) SiO2 etching

- Dry etching (an-isotropic RIE)

- Sidewall spacer formation

- End-point monitoring이 필요

2.

=> nsd(n-MOS source/drain) Mask

1) Photolithography

2) Ion implantation

- As, 70keV, 5x10^15cm^-2

3) PR strip

3.

=> psd(p-MOS source/drain) Mask

1) Photolithography

2) Ion implantation

- BF2, 30keV, 5x10^15cm^-2

3) PR strip

4.

1) cleaning

- SPM, SC1, SC2

2) Rapid thermal annealing

- 목적) dopant의 activation / recrystalization

- ~1000도, 10sec

'반도체 공정' 카테고리의 다른 글

| CMOS process flow_ILD and contact hole/Metal (0) | 2024.05.26 |

|---|---|

| CMOS process flow_Salicide (0) | 2024.05.24 |

| CMOS process flow_gate stack deposition and patterning (0) | 2024.05.22 |

| CMOS process flow_well formation (0) | 2024.05.21 |

| CMOS process flow_isolation (0) | 2024.05.19 |