<MOSFET scaling>

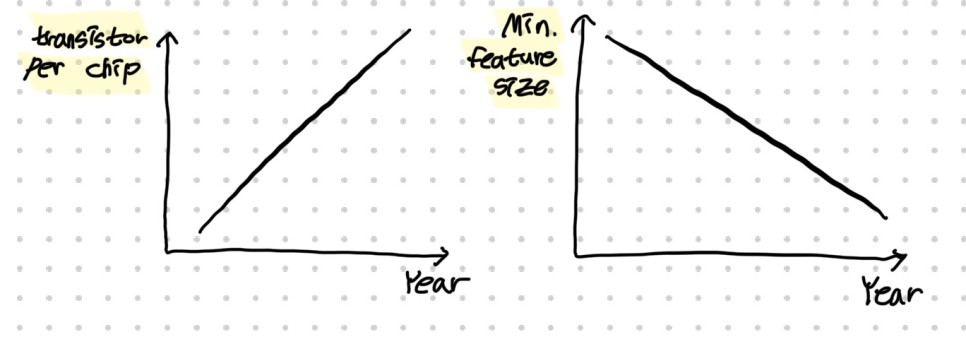

[Moore's law]

매 2년마다 집적회로의 집적도가 2배씩 증가

=> 하지만, 현재에는 한계가 온 상태!

[scaling down의 이점]

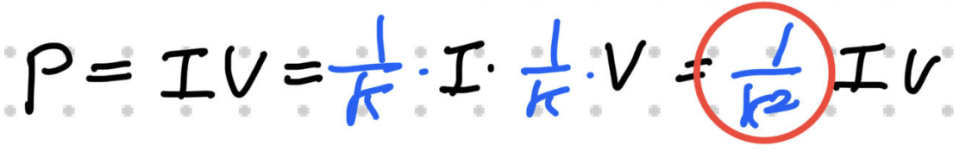

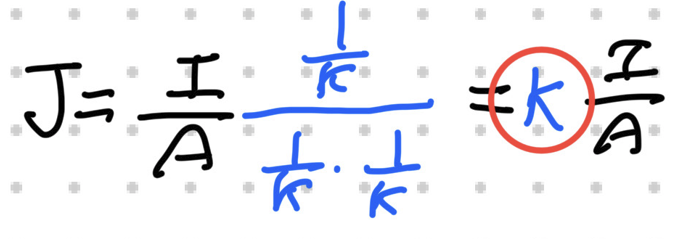

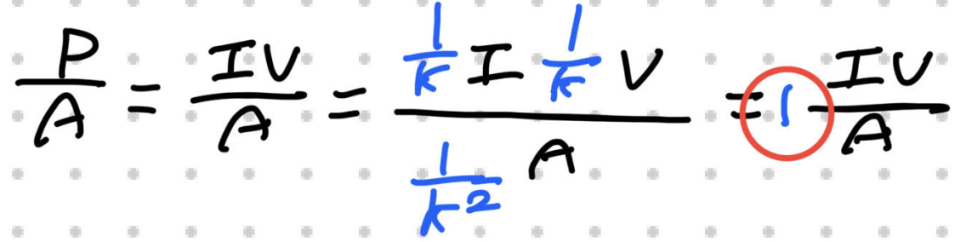

MOSFET의 scale이 K배만큼 감소

-> 'Circuit delay time'은 1/k이 됨

'Power dissipation'은 1/K2이 됨

'current density'는 K가 됨

'Power density'는 1이 됨

=> 집적도, 속도, 전력 소모 등의 향상

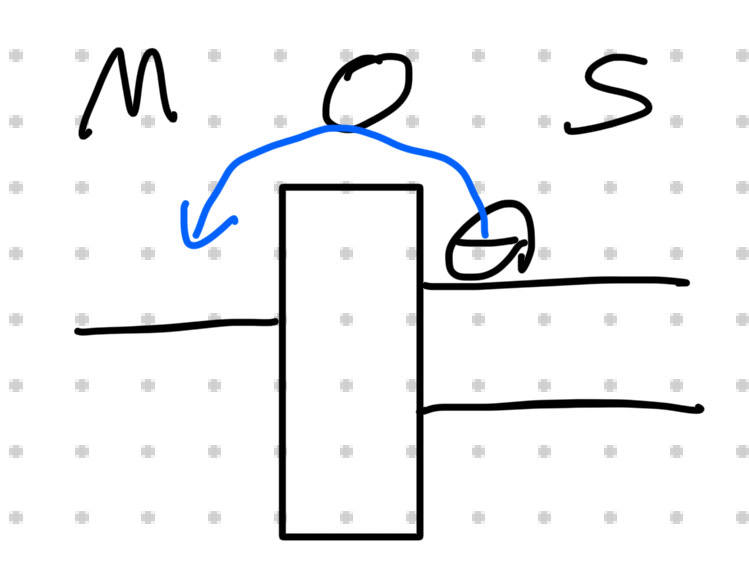

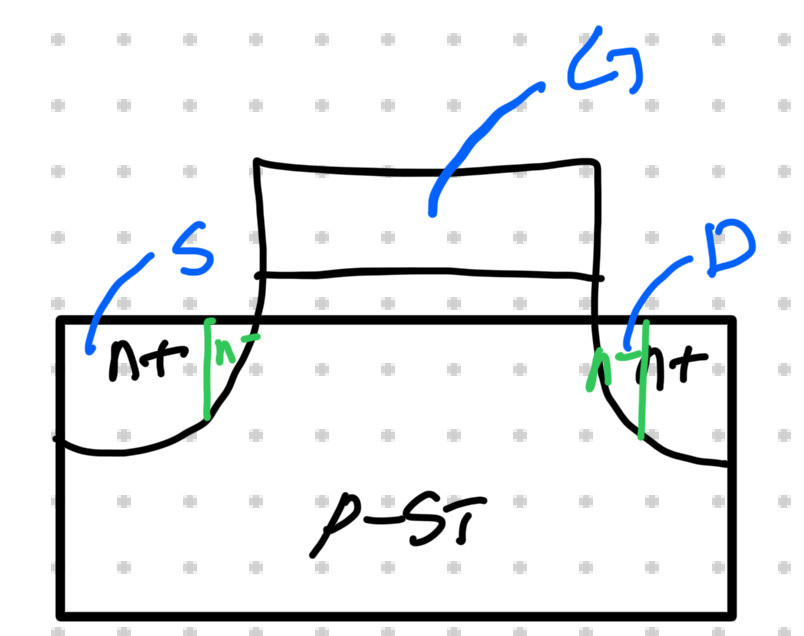

[Short Channel Effect]

MOSFET에서 source와 drain사이의 거리가 좁아짐

-> 전류 조절 기능 상실

<Hot electron effect>

- 원인

- transistor size가 작아짐

-> channel의 길이가 짧아짐

-> electric field가 강해짐

-> 전자가 매우 높은 운동E를 얻음

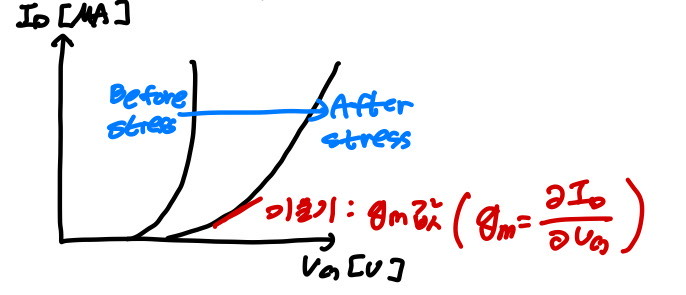

- 영향

- 일부 hot electron

Si-SiO2 간의 포텐셜 장벽을 뛰어 넘음

-> Gate 절연층으로 이동하여, Gate 전류 성분이 될 수 있음

- 일부 전자

게이트 절연층에 trap되어 fixed oxide가 될 수 있음

-> VT 증가

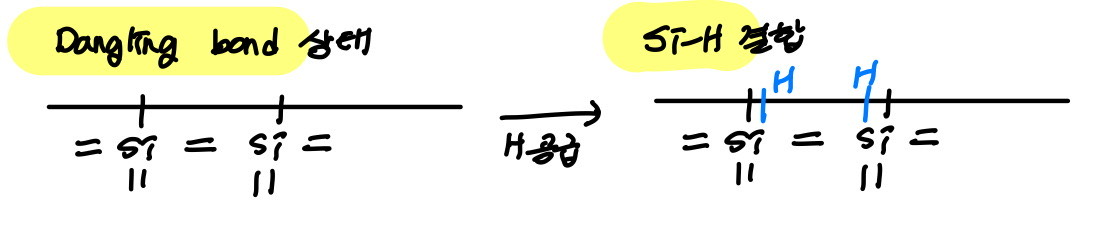

- 큰 에너지를 가진 hot carrier들이 Si-SiO2 경계에서의 Si-H 결합을 깨뜨려 fast interface 상태를 만들 수 있음

cf) Si-H 결합

-> gm과 substrate swing과 같은FET 특성 저하

- 해결방안

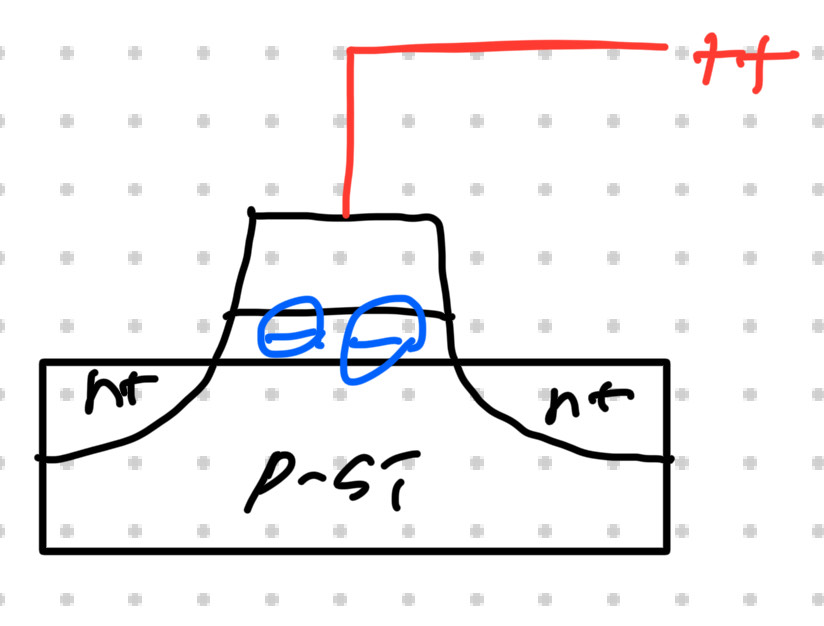

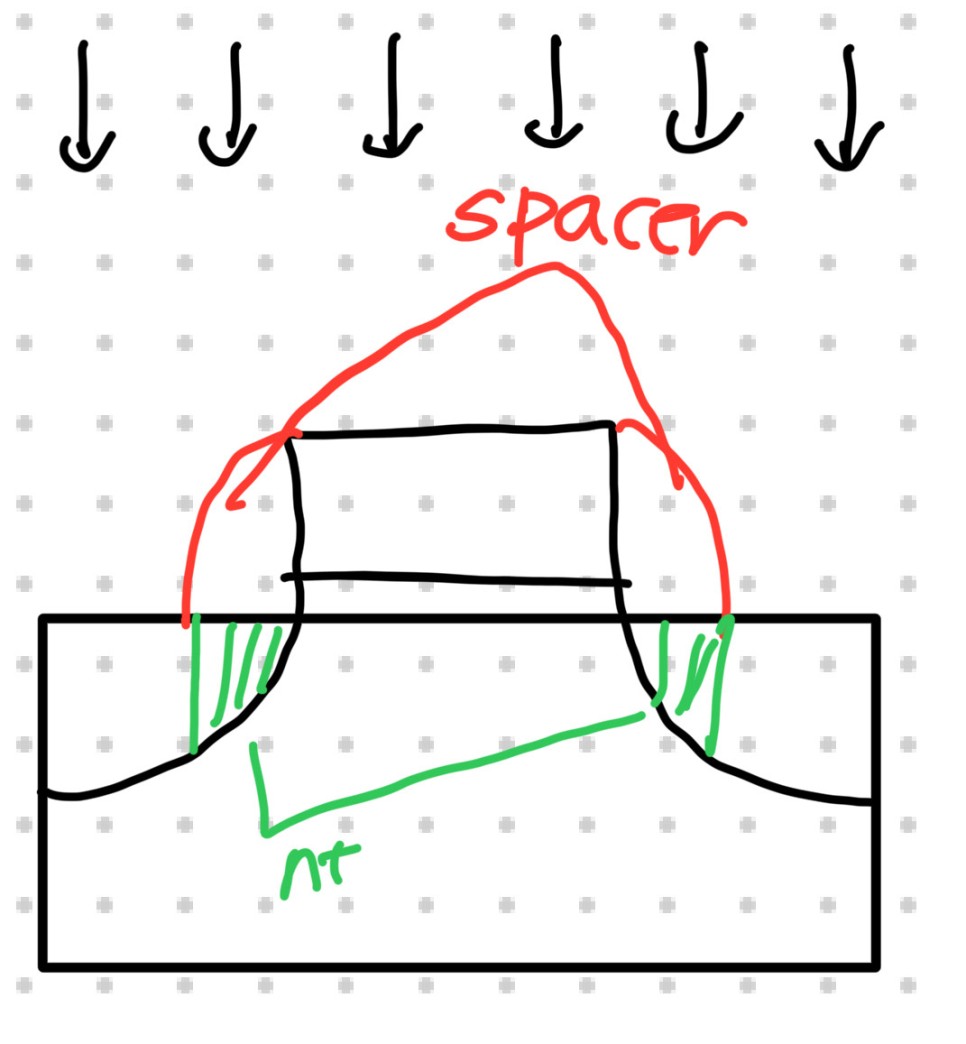

- Lightly Doped Drain (LDD)

channel과 맞닿는 source와 drain 영역의 도핑 농도를 낮게 힘

-> 역방향 전압이 걸린 drain-channel 접합의 depletion 폭이 증가

-> 전기장 완화

- 공정 방법

spacer 활용

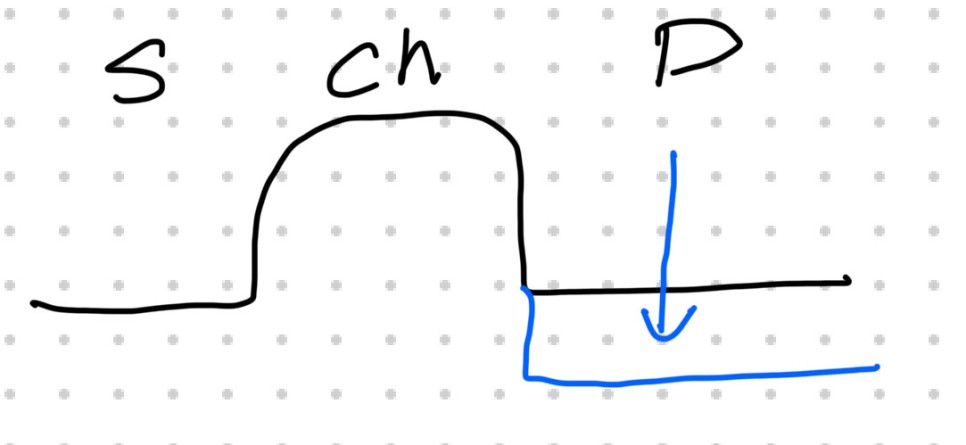

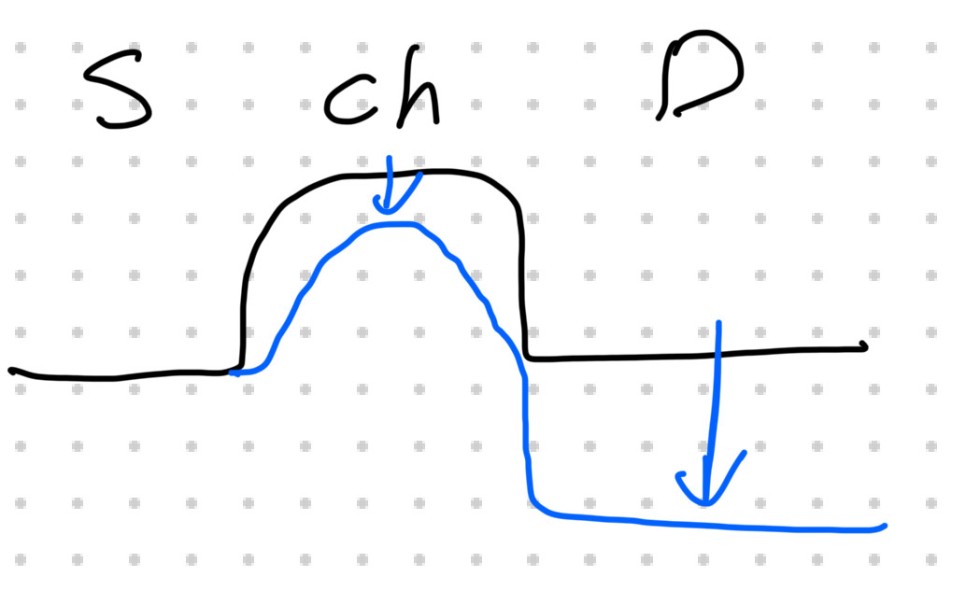

<Drain-induced barrier lowering(DIBL)>

- 원인

- Source와 Drain 사이의 punch-through 또는 breakdown으로 인한 게이트 조절 능력 상실

=> 1) Long Channel

VD가 Source에서 Channel로의 포텐셜 장벽에 영향xxx

2) Short Channel

VD가 증가하면서 drain쪽의 EC를 끌어당겨 Source에서 Channel로의 포텐셜 장벽을 낮아지게 함

- 해결방안

- source와 drain의 도핑을 얕게 생성

- halo impant

부분적으로 P도핑을 해줌으로써 deplation영역을 body쪽으로 확장시키는 것을 방지

- punchthrough가 발생하지 않게 채널 도핑을 충분히 높게 함

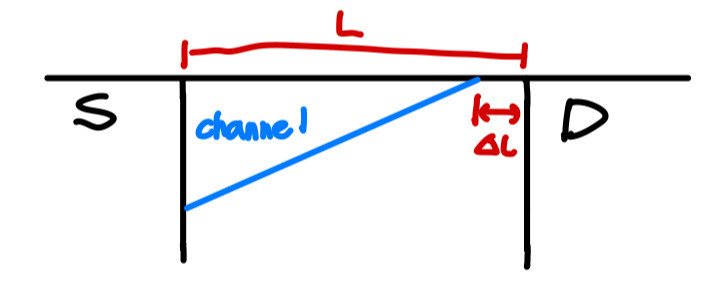

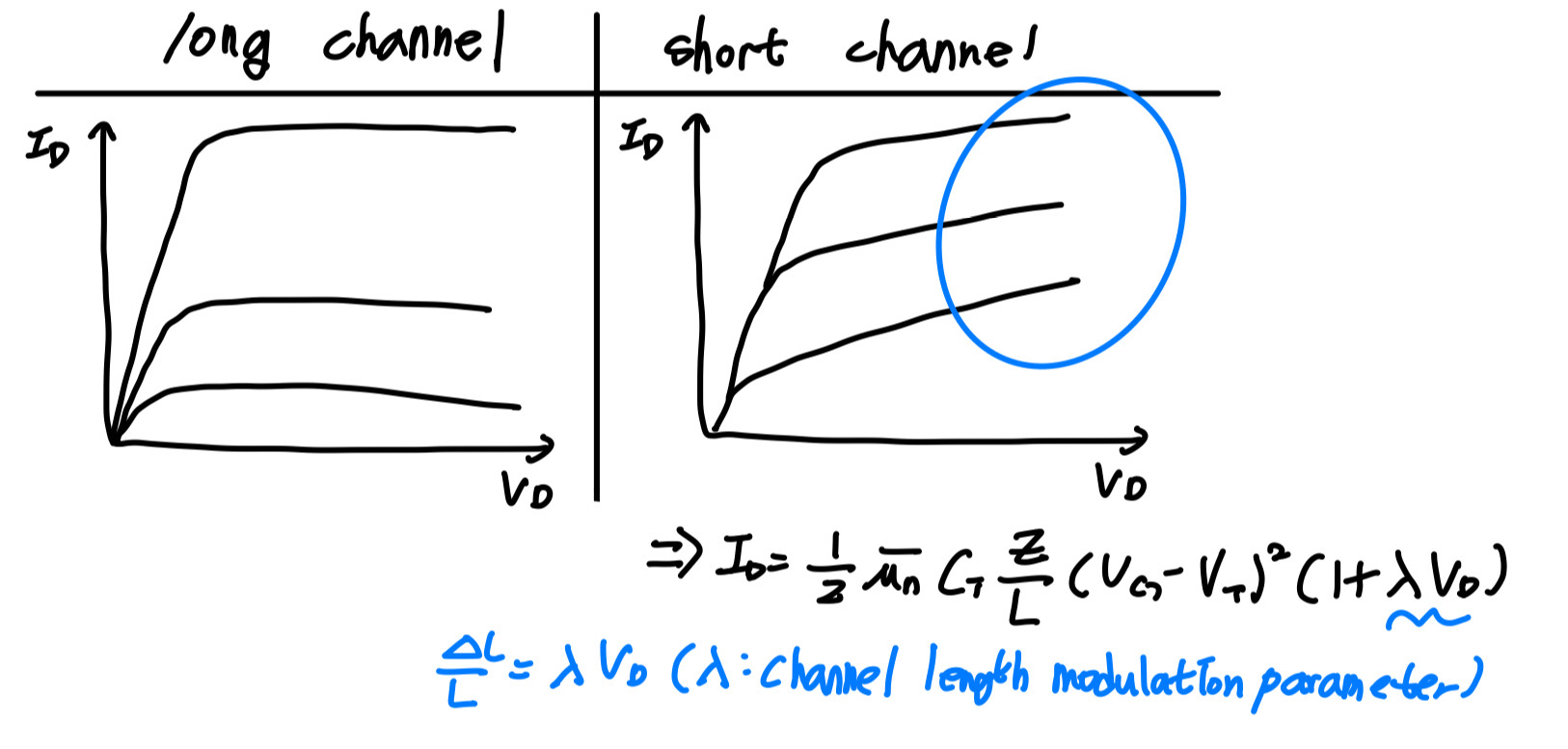

<Short channel length modulation>

- pinch-off 영역의 길이 △L을 고려하면 유효 Channel의 길이는 L- △L

(∵Pinch-off가 발생하면 Channel이 끊기기 때문!)

- short channel의 경우, Saturation 영역에서 전류가 saturation 되지 않고, VD가 증가함에 따라 증가

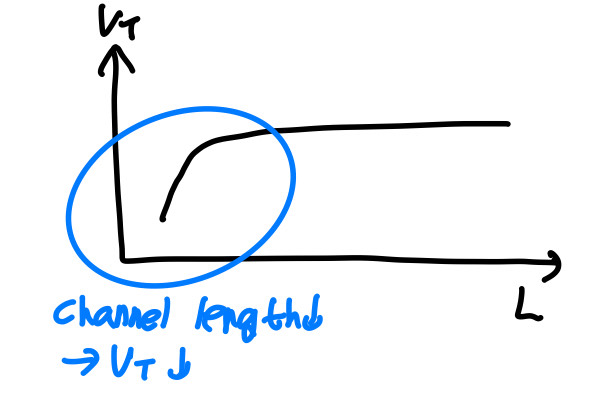

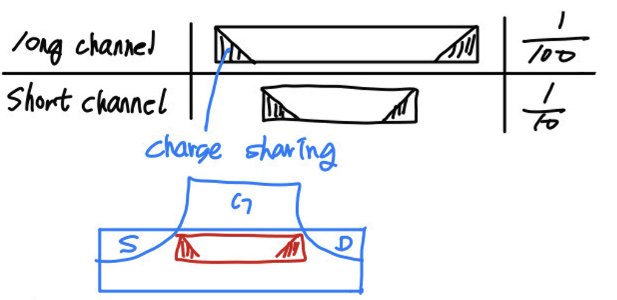

<VT roll-off>

- 채널 길이가 감소함에 따라 VT 감소

- charge sharing

=> Short channel의 경우, gate는 일을 덜 해줘도됨

(∵Source와 Drain이 하는 일 증가)

-> 가해주는 전압이 적어도 채널이 유도됨

'MOSFET' 카테고리의 다른 글

| Advanced MOSFET Structure (0) | 2024.01.26 |

|---|---|

| 문턱전압조절 (0) | 2024.01.26 |

| MOSFET ID-VD 특성 / ID-VG 특성 (0) | 2024.01.26 |

| MOS cap C-V 특성 (0) | 2024.01.26 |

| 이상적인 MOS cap (0) | 2024.01.26 |